# Control Integrated POwer System (CIPOS<sup>TM</sup>)

Reference Board for IGCM06B60GA

AN-CIPOS mini-2-Reference Board-2

Authors: JunHo Leeg, JunBae Lee and DaeWoong Chung

http://www.lspst.com

For Power Management Application

| Revision History: | 2010-10                                      | V0.5 |

|-------------------|----------------------------------------------|------|

| Previous Version: | Ver. 0.4                                     |      |

| Page              | Subjects (major changes since last revision) |      |

|                   |                                              |      |

#### **Edition 2010-06**

Published by LS Power Semitech Co., Ltd. Seoul, Korea © LS Power Semitech Co., Ltd. All Rights Reserved.

#### Attention please!

THE INFORMATION GIVEN IN THIS APPLICATION NOTE IS GIVEN AS A HINT FOR THE IMPLEMENTATION OF THE LS POWER SEMITECH CO., LTD. COMPONENT ONLY AND SHALL NOT BE REGARDED AS ANY DESCRIPTION OR WARRANTY OF A CERTAIN FUNCTIONALITY, CONDITION OR QUALITY OF THE LS POWER SEMITECH CO., LTD. COMPONENT. THE RECIPIENT OF THIS APPLICATION NOTE MUST VERIFY ANY FUNCTION DESCRIBED HEREIN IN THE REAL APPLICATION. LS POWER SEMITECH CO., LTD. HEREBY DISCLAIMS ANY AND ALL WARRANTIES AND LIABILITIES OF ANY KIND (INCLUDING WITHOUT LIMITATION WARRANTIES OF NON-INFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS OF ANY THIRD PARTY) WITH RESPECT TO ANY AND ALL INFORMATION GIVEN IN THIS APPLICATION NOTE.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest LS Power Semitech Co., Ltd. office (<a href="https://www.lspst.com">www.lspst.com</a>).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest LS Power Semitech Co., Ltd. office.

LS Power Semitech Co., Ltd. components may only be used in life-support devices or systems with the express written approval of LS Power Semitech Co., Ltd., if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# Control Integrated POwer System (CIPOS<sup>™</sup>) Reference Board for CIPOS<sup>™</sup> IGCM06B60GA

#### **Table of contents**

| 1     | Introduction                                     | 4        |

|-------|--------------------------------------------------|----------|

| 2     | Schematic                                        | <u> </u> |

| 3     | External Connection                              |          |

| 3.1   | Signal Connector (J1, 2.5mm pitch connector)     | 6        |

| 3.2   | Power Connector                                  | 6        |

| 4     | Key Parameters Design Guide                      | 7        |

| 4.1   | Circuit of Input Signals (LIN, HIN)              | 7        |

| 4.2   | Bootstrap Capacitor                              | 7        |

| 4.3   | Internal Bootstrap Functionality Characteristics |          |

| 4.4   | Over Current Protection                          |          |

| 4.4.1 | Shunt Resistor Selection                         | Ç        |

| 4.4.2 | Delay Time                                       | 1C       |

| 4.5   | Temperature Monitor and Protection               | 11       |

| 5     | Part list                                        | 12       |

| 6     | PCB Design Guide                                 | 13       |

| 6.1   | Layout of Reference Board                        | 13       |

| 7     | Reference                                        | 14       |

### 1 Introduction

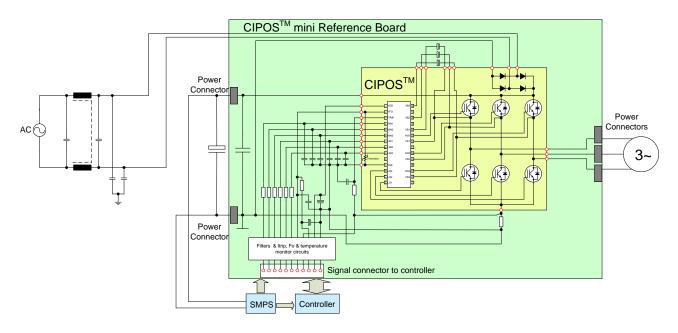

This reference board is composed of the IGCM06B60GA, its minimum peripheral components and single shunt resistor. It is designed for customers to evaluate the performance of CIPOS<sup>TM</sup> with simple connection of the control signals and power wires. Figure 1 shows the external view of reference board.

This application note also describes how to design the key parameters and PCB layout.

Figure 1. Reference board for IGCM06B60GA

Figure 2. Application example

Reference Board Guide 4 Oct. 2010

#### 2 Schematic

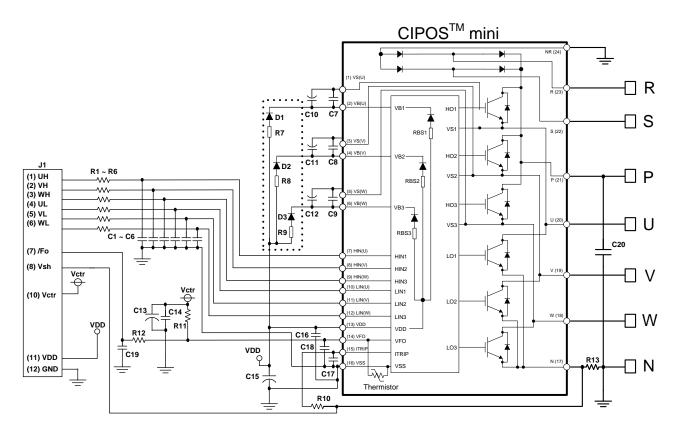

Figure 3 shows a circuitry of the reference board for IGCM06B60GA.

The reference board consists of interface circuit, bootstrap circuit, snubber capacitor, short-circuit protection, fault output circuit and single shunt resistor.

Figure 3. Circuit of the reference board

Note: Vctr denotes the controller supply voltage such as 5V or 3.3V.

It is optional to use external bootstrap circuit together with internal one as shown in dot line, in case that smaller bootstrap resistor is necessary.

Reference Board Guide 5 Oct. 2010

# 3 External Connection

# 3.1 Signal Connector (J1, 2.5mm pitch connector)

| Pin | Name   | Description                               |

|-----|--------|-------------------------------------------|

| 1   | HIN(U) | High side control signal input of U phase |

| 2   | HIN(V) | High side control signal input of V phase |

| 3   | HIN(W) | Low side control signal input of W phase  |

| 4   | LIN(U) | Low side control signal input of U phase  |

| 5   | LIN(V) | Low side control signal input of V phase  |

| 6   | LIN(W) | Low side control signal input of W phase  |

| 7   | /Fo    | Fault output signal / Temperature monitor |

| 8   | Vsh    | Shunt voltage sensing signal              |

| 9   | Vctr   | External control voltage (5V or 3.3V)     |

| 10  | VDD    | External 15V supply voltage               |

| 11  | GND    | Ground                                    |

### 3.2 Power Connector

| Pin | Description                                 |

|-----|---------------------------------------------|

| U   | Output terminal of U phase                  |

| V   | Output terminal of V phase                  |

| W   | Output terminal of W phase                  |

| Р   | Positive terminal of DC link voltage        |

| N   | Negative terminal of DC link voltage        |

| R   | Single phase diode bridge rectifier R input |

| S   | Single phase diode bridge rectifier S input |

Reference Board Guide 6 Oct. 2010

# 4 Key Parameters Design Guide

#### 4.1 Circuit of Input Signals (LIN, HIN)

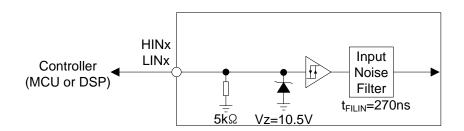

The input signals can be either TTL- or CMOS-compatible. The logic levels can go down to 3.3V. The maximum input voltage of the pins is internally clamped to 10.5V. However, the recommended voltage range of input voltage is up to 5V. The control pins LIN and HIN are active high.

They have an internal pull-down structure with a pull-down resistor value of nominal  $5k\Omega$ . The input noise filter inside CIPOS<sup>TM</sup> suppresses short pulse and prevents the driven IGBT from unintentional operation. The input noise filter time ( $t_{FLIN}$ ) is typically 270ns. This means that an input signal must stay on more than 270ns so that the input signal can be processed correctly. CIPOS<sup>TM</sup> can be connected directly to controller without external input RC filter thanks to the internal pull down resistor and input noise filter as shown in Figure 4.

Figure 4. Filter of input signals and pull-down circuit

#### 4.2 Bootstrap Capacitor

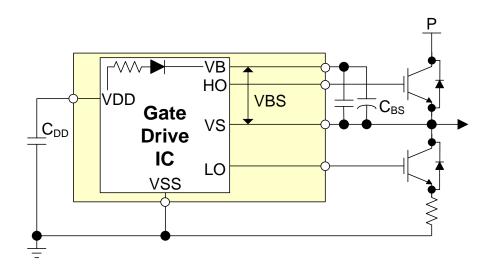

Bootstrapping is a common method of pumping charges from a low potential to a higher one. With this technique a supply voltage for the floating high side sections of the gate drive can be easily established according to Figure 5. It is only the effective circuit shown for one of the three half bridges. The bootstrap functionality is composed internally to limit current. Please refer to the datasheet and application note for bootstrapping method in detail.

Figure 5. Bootstrap circuit for the supply of a high side gate drive

Reference Board Guide 7 Oct. 2010

# Control Integrated POwer System (CIPOS<sup>™</sup>) Reference Board for CIPOS<sup>™</sup> IGCM06B60GA

A low leakage current of the high side section is very important in order to keep the bootstrap capacitors small. The C<sub>BS</sub> discharges mainly by the following mechanisms:

- Quiescent current to the high side circuit in the IC

- Gate charge for turning high side IGBT on

- Level-shift charge required by level shifters in the IC

- Leakage current in the bootstrap diode

- C<sub>BS</sub> capacitor leakage current (ignored for non-electrolytic capacitor)

- Bootstrap diode reverse recovery charge

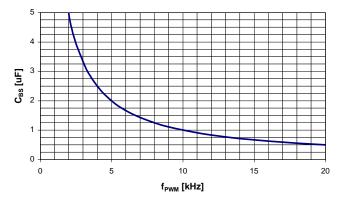

The calculation of the bootstrap capacitor results in

$$C_{BS} = \frac{I_{leak} \times t_{P}}{\Delta V_{BS}}$$

with  $I_{leak}$  being the maximum discharge current of  $C_{BS}$ ,  $t_P$  the maximum on pulse width of high side IGBT and  $\Delta V_{BS}$  the voltage drop at the bootstrap capacitor within a switching period.

Practically, the recommended leakage current is 1mA of I<sub>leak</sub> for CIPOS<sup>TM</sup>.

Figure 6 shows the curve corresponding to above equation for a continuous sinusoidal modulation, if the voltage ripple  $\Delta$  V<sub>BS</sub> is 0.1V. The recommended bootstrap capacitance for a continuous sinusoidal modulation method is therefore in the range up to 4.7 $\mu$ F for most switching frequencies. In other PWM method case like a discontinuous sinusoidal modulation, t<sub>P</sub> must be set the longest period of the low side IGBT off.

Figure 6. Size of the bootstrap capacitor as a function of the switching frequency fpwm

#### 4.3 Internal Bootstrap Functionality Characteristics

CIPOS<sup>TM</sup> includes three bootstrap functionalities in internal drive IC, which consist of three diodes and three resistors, as shown in Figure 5. Typical value of internal bootstrap resistor is  $40\Omega$ . For more information, please refer to the below table. It's noted that  $R_{BS2}$  and  $R_{BS3}$  have same value to  $R_{BS1}$ .

| Description                     | Condition                                                                                                                                                        | Symbol             | Min. | Тур.                 | Max. | Unit |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|----------------------|------|------|

| Repetitive peak reverse voltage |                                                                                                                                                                  | $V_{RRM}$          | 600  |                      |      | V    |

| Bootstrap resistance of U-phase | VS2 or VS3=300V, T <sub>J</sub> =25°C<br>VS2 and VS3=0V, T <sub>J</sub> =25°C<br>VS2 or VS3=300V, T <sub>J</sub> =125°C<br>VS2 and VS3=0V, T <sub>J</sub> =125°C | R <sub>BS1</sub>   |      | 35<br>40<br>50<br>65 |      | Ω    |

| Reverse recovery                | I <sub>F</sub> =0.6A, di/dt=80A/μs                                                                                                                               | t <sub>rr_BS</sub> |      | 50                   |      | ns   |

| Forward voltage drop            | I <sub>F</sub> =20mA, VS2 and VS3=0V                                                                                                                             | V <sub>F_BS</sub>  |      | 2.6                  |      | V    |

Reference Board Guide 8 Oct. 2010

#### 4.4 Over Current Protection

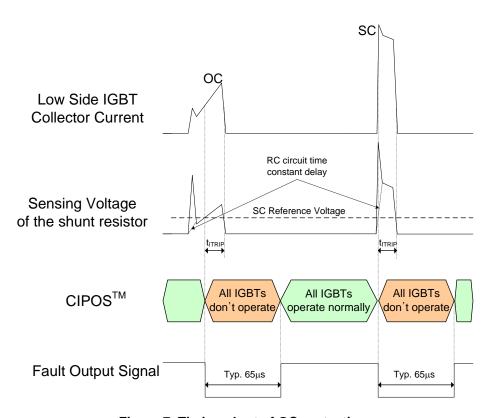

The OC (Over Current) protection level is decided by ITRIP positive going threshold voltage  $V_{IT,TH+}$  in CIPOS<sup>TM</sup> and shunt resistance. When ITRIP voltage exceeds  $V_{IT,TH+}$ , CIPOS<sup>TM</sup> turns off 6 IGBTs and fault-output is activated during fault-output duration time, typically 65us.

Figure 7. Timing chart of OC protection

#### 4.4.1 Shunt Resistor Selection

The value of shunt resistor is calculated by the following equation.

$$R_{SH} = \frac{V_{IT,TH+}}{I_{OC}}$$

Where  $V_{IT,TH+}$  is the ITRIP positive going threshold voltage of CIPOS<sup>TM</sup> and  $I_{OC}$  is the current of SC detection level.  $V_{IT,TH+}$  is  $0.47V_{typ.}$ .

The maximum value of OC protection level should be set less than the repetitive peak collector current in the datasheet considering the tolerance of shunt resistor.

For example, the maximum peak collector current of IGCM06B60GA is 12A<sub>peak</sub>,

$$R_{SH(min)} = \frac{0.47}{12} = 0.0392\Omega$$

Reference Board Guide 9 Oct. 2010

# Control Integrated POwer System (CIPOS<sup>™</sup>) Reference Board for CIPOS<sup>™</sup> IGCM06B60GA

So the recommended value of shunt resistor is over 40m $\Omega$  for IGCM06B60GA. For the power rating of the shunt resistor, the below lists should be considered.

- Maximum load current of inverter (I<sub>rms</sub>)

- Shunt resistor value at Tc=25°C (R<sub>SH</sub>)

- Power derating ratio of shunt resistor at T<sub>SH</sub>=100°C

- Safety margin

And the power rating is calculated by following equation.

$$P_{SH} = \frac{I_{rms}^{2} R_{SH} \times marigin}{Derating ratio}$$

For example, In case of IGCM06B60GA and  $R_{SH}$ =40m $\Omega$

- Max. load current of inverter : 4A<sub>rms</sub>

- Power derating ratio of shunt resistor at T<sub>SH</sub>=100°C: 80%

- Safety margin: 30%

$$P_{SH} = \frac{4^2 \times 0.04 \times 1.3}{0.8} = 1.0W$$

So the proper power rating of shunt resistor is over 1W.

Based on the previous equations, conditions and calculation method, minimum shunt resistance and resistor power according to all kinds of IGCM06B60GA products are introduced as shown in below table. It's noted that a proper resistance and its power over than minimum values should be chosen considering over-current protection level required in the application set.

| Product     | Maximum Peak | Minimum Shunt   | Minimum Shunt Resistor |

|-------------|--------------|-----------------|------------------------|

|             | Current      | Resistance, RSH | Power, PSH             |

| IGCM06B60GA | 12           | 40m $Ω$         | 1W                     |

#### 4.4.2 Delay Time

The RC filter should be necessary in OC sensing circuit to prevent malfunction of OC protection from noise interference. The RC time constant is determined by applying time of noise and the withstand time capability of IGBT. When the current on shunt resistor exceeds OC protection level ( $I_{OC}$ ), this voltage is applied to the ITRIP pin of CIPOS<sup>TM</sup> via the RC filter. The filter delay time ( $I_{Filter}$ ) that the input voltage of ITRIP pin rises to the ITRIP positive threshold voltage is caused by RC filter time constant. In addition there is the shutdown propagation delay of Itrip ( $I_{ITRIP}$ ). Please refer to the below table.

| Item                                              |            | Condition                                         | Min. | Тур. | Max. | Unit |

|---------------------------------------------------|------------|---------------------------------------------------|------|------|------|------|

| Shut down propagation delay (t <sub>ITRIP</sub> ) | GCM06x60GA | $I_{out}$ =4A, from $V_{IT,TH+}$ to 10% $I_{out}$ | -    | 1300 | -    | ns   |

Therefore, the total delay time from occurrence of OC to shutdown of the IGBT gate becomes

$$t_{total} = t_{Filter} + t_{ITRIP}$$

Shut down propagation delay is in inverse proportion to the current range, therefore  $t_{ITRIP}$  is reduced at higher current condition than condition of table 14. The total delay must be less than  $5\mu s$  of short circuit withstand time ( $t_{SC}$ ) in datasheet. Thus, RC time constant should be set in the range of  $1\sim2\mu s$ . It is recommended that R10 of  $1.8k\Omega$  and C17 of 1nF.

Reference Board Guide 10 Oct. 2010

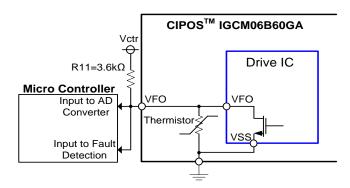

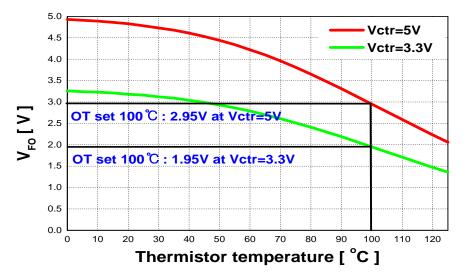

## 4.5 Temperature Monitor and Protection

In case of CIPOS<sup>TM</sup>, built-in thermistor ( $85k\Omega$  at  $25^{\circ}$ C) is connected between VFO and VSS. The typical application circuit is like Figure 8 where the VFO pin is used for both thermistor temperature detection and fault detection. The voltage of VFO pin decreases as the thermistor temperature increases due to external pull-up resistor. It is noted that the voltage variation of VFO pin due to temperature variation should be always higher than the fault detection level of micro controller. In this reference board, the pull-up resistor is set to  $3.6k\Omega$  so that the VFO voltage becomes 2.95V and 1.95V respectively for 5V and 3.3V control voltage (Vctr) when the temperature of thermistor is  $100^{\circ}$ C as shown in Figure 9.

Figure 8. Temperature monitor with built in thermistor and pull up resistor

Figure 9. Voltage of V<sub>FO</sub> according to the temperature

Reference Board Guide 11 Oct. 2010

# 5 Part list

| Symbol             | Components      | Note                                          |

|--------------------|-----------------|-----------------------------------------------|

| R1 ~ R6            | 100Ω, 1/8W, 5%  | Series resistors for input voltage            |

| R7 ~ R9            | No Connection   | Note 1                                        |

| R10                | 1.8kΩ, 1/8W, 1% | Series resistor for current sensing voltage   |

| R11                | 3.6kΩ, 1/8W, 1% | Pull-up resistor for fault output voltage     |

| R12                | 1kΩ, 1/8W, 5%   | Series resistor for fault output voltage      |

| R13                | Content 4.4.1   | Current sensing resistor                      |

| C1 ~ C6            | 1nF, 25V        | Bypass capacitors for input voltage           |

| C7 ~ C9            | 0.1uF, 25V      | Bypass capacitors for high side bias voltage  |

| C10 ~ C12          | 22uF, 35V       | Bootstrap capacitors                          |

| C13                | 100uF, 35V      | Source capacitor for 5 or 3.3V supply voltage |

| C14                | 0.1uF, 35V      | Bypass capacitor for 5 or 3.3V supply voltage |

| C15                | 220uF, 35V      | Source capacitor for VDD supply voltage       |

| C16                | 0.1uF, 35V      | Bypass capacitor for VDD supply voltage       |

| C17                | 1nF, 25V        | Bypass capacitor for current sensing voltage  |

| C18                | 1nF, 16V        | Bypass capacitor for fault output voltage     |

| C19                | 1nF, 16V        | Bypass capacitor for fault output voltage     |

| C20                | 0.1uF, 630V     | Snubber capacitor                             |

| D1 ~ D3            | No Connection   | Note 1                                        |

| J1                 | SMW250-11P      | Signal & Power supply connector               |

| U, V, W, P, N R, S | Fasten Tap      | Power terminals                               |

Note 1: It is optional to use external bootstrap circuit together with internal one, in case that smaller bootstrap resistor is necessary.

Reference Board Guide 12 Oct. 2010

# 6 PCB Design Guide

In general, there are several issues to be considered when designing an inverter board as below lists.

- Low stray inductive connection

- Isolation distance

- Component placement

This chapter explains above considerations and method for the layout design.

#### 6.1 Layout of Reference Board

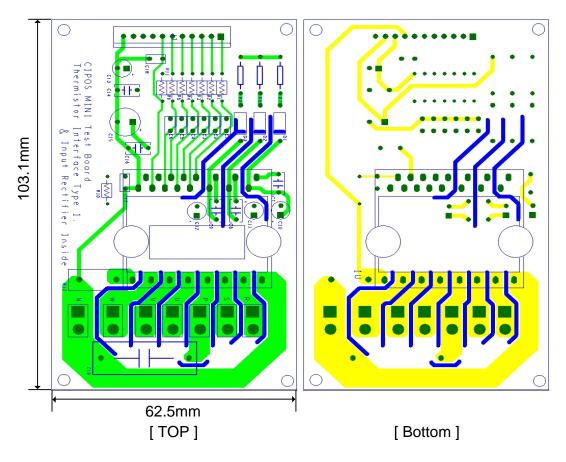

Figure 10. Layout of reference board for IGCM06B60GA

#### Note.

- 2. The connection between emitters of CIPOS<sup>TM</sup> (N) and shunt resistor should be as short and as wide as possible.

- 3. It is recommended that ground pin of micro-controller be directly connected to VSS pin. Signal ground and power ground should be as short as possible and connected at only one point via the capacitor (C16).

- 4. All of the bypass capacitors should be placed as close to the pins of CIPOS<sup>™</sup> as possible.

- 5. The capacitor (C17) for shunt voltage sensing should be placed as close to ITRIP and VSS pins as possible.

- 6. In order to detect sensing voltage of the shunt resistor exactly, both sensing and ground patterns should be connected at pins of the shunt resistor and should not be overlapped with any patterns for load current as shown in Figure 10.

- 7. The snubber capacitor (C19) should be placed as close to the terminals as possible.

- 8. The power patterns of U, V, W, P,N,R and S should be designed on both layer with via to cover the high current and there should be kept the isolation distance among the power patterns over 2.54mm.

- 9. There are milling profiles in blue line to keep the isolation distance

- 10. All components except IGCM06B60GA are placed on the top layer.

Reference Board Guide 13 Oct. 2010

| 7       | Reference                                                                                                         |

|---------|-------------------------------------------------------------------------------------------------------------------|

| [1]     | <b>LS Power Semitech:</b> CIPOS <sup>™</sup> IGCM06B60GA; Preliminary Datasheet Ver. 0.2; LS Power Semitech, 2010 |

|         |                                                                                                                   |

|         |                                                                                                                   |

|         |                                                                                                                   |

|         |                                                                                                                   |

|         |                                                                                                                   |

|         |                                                                                                                   |

|         |                                                                                                                   |

|         |                                                                                                                   |

|         |                                                                                                                   |

|         |                                                                                                                   |

|         |                                                                                                                   |

| http:// | www.lspst.com                                                                                                     |

|         |                                                                                                                   |