**Preliminary**

## **Data Sheet IGD616**

# Single Channel SCALE IGBT Driver Core

A successor to the IGD608/615 single-channel gate driver cores for 1200V and 1700V IGBTs

The IGD616 is a highly-integrated single IGBT driver core based on CONCEPT's proprietary SCALE technology which has been established on the market as an industrial standard since 1999.

The IGD616 has been developed for direct replacement of IGD608 and IGD615. It features a dedicated set of compatible items to ease seamless transition in existing designs. Its drive power and performance exceed prior specifications such that now one single driver core IGD616 will cover the range of both IGD608 and IGD615 at a superior reliability level.

The driver core is optimized to match various IGBTs and applications from 100A / 1200V to 1000A / 1700V and beyond.

#### **Features**

- S Applications

- Direct replacement of IGD615

- Highly approved SCALE technology

- Non-inverting or optionally inverting inputs

- ✓ Gate drive capability 16A, 6W

- ✓ Typical delay time of 315ns

- Power supply voltage monitoring set to 11.5V

- ✓ Superior EMC (dv/dt > 100V/ns, ESD > 2kV)

- Highly flexible single-channel design

- Command signal transmitted via transformer interface

- Fault signal via transformer interface or optional optocoupler

- 22ms blocking time at fault with custom-specific time options

- Driving 1200V and 1700V IGBTs

- Switching DC to 150 kHz

- ✓ Duty cycle 0 ... 100%

- ✓ Operating temp. -40 ... +85 °C

- Two-level topologies

- AC drives, SMPS, etc.

- ✓ Industry, traction, wind power

### Compatibility to IGD608 / IGD615 Gate Drivers

The IGD616 is available with different options covering a dedicated set of compatible items. In this data sheet, the text referring to critical compatible items is underlined.

Option N and Option I select between non-inverting and inverting inputs respectively. It is no longer possible to interchange the IN+ and IN- inputs to invert the logic.

On the secondary side, any fault state is extended by a period known as the command blocking time. During this time, the driver is kept in the off-state. The command blocking time is set at the factory to a nominal value of 22ms. Other values upon request. It is no longer possible for the application to adjust the blocking time.

For option T, the signal transformer interface is used to transfer the secondary fault signal to the primary side. This transfer may be performed at each change in the command signal, but only during the blocking time. For option C, an optocoupler is used to transfer the secondary-side fault state to the primary side within a delay of less than several microseconds. The initial creepage distance and the maximum operating voltage are reduced by the optocoupler.

For a summary, refer to the Ordering Information section on the last page.

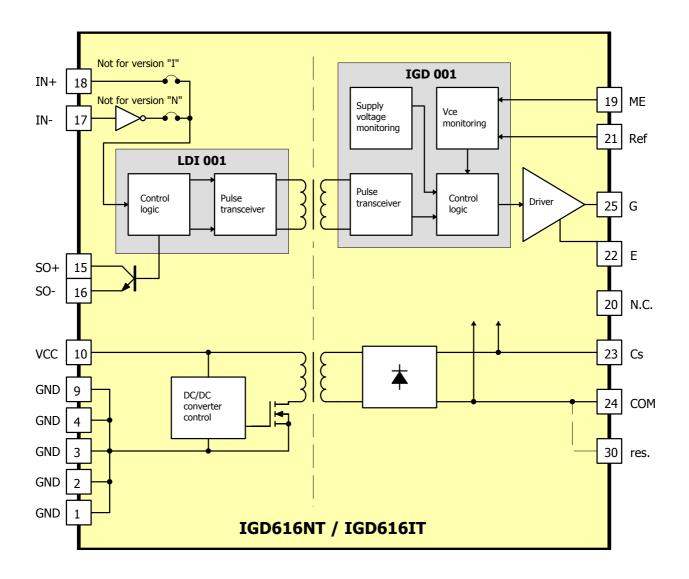

## **Block Diagram of IGD616 Option T**

Fig. 1 Block diagram of the IGD616 (option T, i.e. fault signal via signal transformer interface). Non-inverting inputs (option N) or inverting inputs (option I). Not connected pins are designated as N.C.

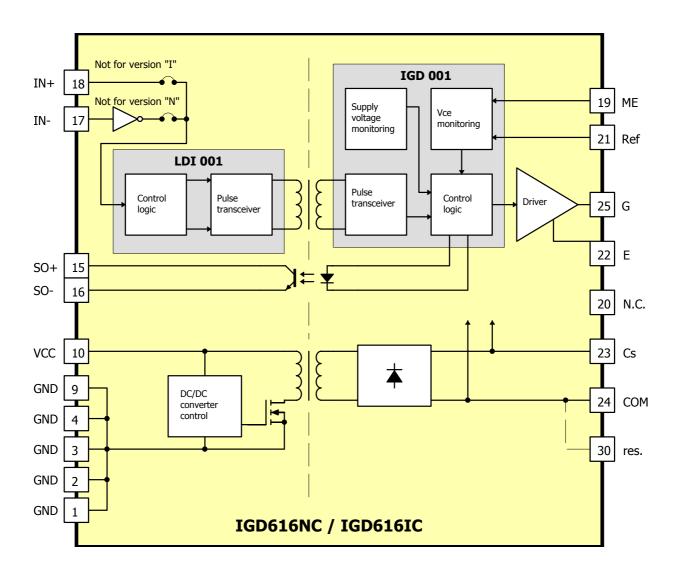

## **Block Diagram of IGD616 Option C**

Fig. 2 Block diagram of the IGD616 (option C, i.e. fault signal via optocoupler). Non-inverting inputs (option N) or inverting inputs (option I). Not connected pins are designated as N.C.

## **Pin Description**

| No.   | Pin Na | ame Function                                                                          |

|-------|--------|---------------------------------------------------------------------------------------|

| 1-16  |        | Primary-side terminal                                                                 |

| 1- 4  | GND    | Power supply and logic ground                                                         |

| 5- 8  |        | Physically not present                                                                |

| 9     | GND    | Power supply and logic ground                                                         |

| 10    | VCC    | Power supply positive voltage referenced to pin GND                                   |

| 11-14 |        | Physically not present                                                                |

| 15    | SO+    | Status output positive voltage referenced to pin SO-                                  |

| 16    | SO-    | Status output negative voltage referenced to pin SO+                                  |

| 17    | IN-    | For option I: Inverting input referenced to GND                                       |

|       |        | For option N: Functionless CMOS input (must be terminated to logic high or logic low) |

| 18    | IN+    | For option I: Functionless CMOS input (must be terminated to logic high or logic low) |

|       |        | For option N: Non-inverting input referenced to GND                                   |

|       |        |                                                                                       |

| 19-36 |        | Secondary-side terminal                                                               |

| 19    | ME     | IGBT collector voltage monitoring input referenced to pin E                           |

| 20    | N.C.   | Not connected / reserved for future use                                               |

| 21    | REF    | Reference voltage for short-circuit monitoring referenced to pin E                    |

| 22    | Е      | IGBT emitter terminal                                                                 |

| 23    | Cs     | 16.4V nominal voltage power supply referenced to pin COM                              |

| 24    | COM    | Common terminal (secondary side ground)                                               |

| 25    | G      | Gate driver output                                                                    |

| 26-29 |        | Physically not present                                                                |

| 30-36 | N.C.   | Not connected / reserved for future use                                               |

Not connected pins are designated as N.C.

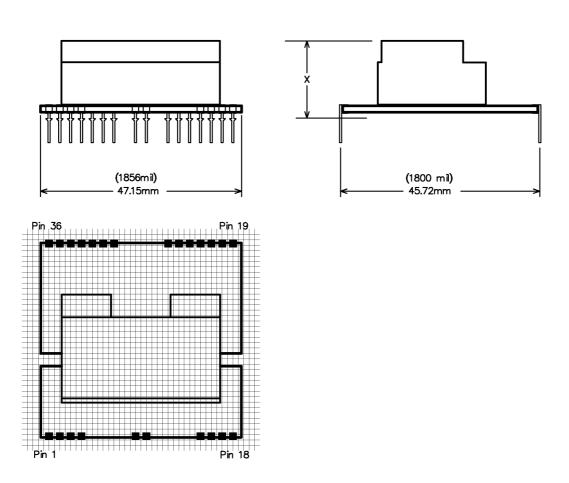

#### **Mechanical Data**

Fig. 3 Footprint of IGD616. Grid is 1.27mm (50mil). Recommended diameter of solder pad is 1.6mm. Recommended diameter of drill holes is 1.0mm.

Height X = 18.5mm +/- 0.5mm for option T.

Height X = 20.5mm +/- 0.5mm for option C.

## **Absolute Maximum Ratings**

| Parameter                     | Condition/remark                         | Min.  | Max. l | Jnits |

|-------------------------------|------------------------------------------|-------|--------|-------|

| Primary supply voltage VCC    | To GND                                   | 0     | 16     | V     |

| Pin G IGBT gate pulse current |                                          | -16.0 | +16.0  | Α     |

| Maximum Pulse Gate Charge Qg  | without external Capacitors (note 9)     |       | 5.1    | μC    |

|                               | external Capacitors < 100µF (notes 2, 9) |       | 55     | μC    |

| IGBT average gate power       |                                          |       | 6.0    | W     |

| Primary supply current        | Continuous, after startup sequence       |       | 550    | mA    |

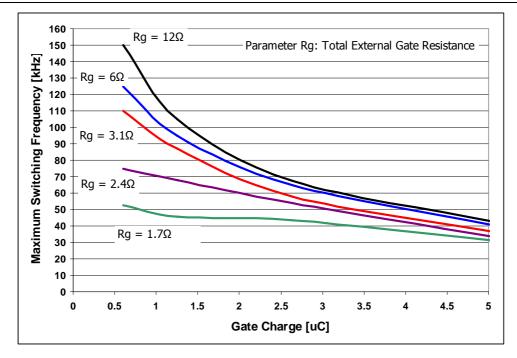

| IGBT switching frequency      | see diagram                              |       | 150    | kHz   |

Fig. 4 Maximum allowed switching frequency vs. total gate charge Parameter Rg (total external gate resistance); unforced convection (cooling in free air)

| Pin IN voltage                |                      | 0   | VCC | V  |

|-------------------------------|----------------------|-----|-----|----|

| Pin SO voltage                |                      | 0   | VCC | V  |

| Pins REF, ME voltages         | To COM               | 0   | VCC | V  |

| Operating ambient temperature | Continuous           | -40 | 85  | °C |

| Storage ambient temperature   |                      | -45 | 90  | °C |

| Lead temperature              | Soldering, 5 seconds |     | 260 | °C |

Unless otherwise specified, all data refer to a primary supply voltage of 15V and an ambient temperature of +85°C.

## **Recommended Operating Conditions**

| Parameter                      | Condition/remark | Min. | Max. Units |

|--------------------------------|------------------|------|------------|

| Primary supply voltage VCC     | To GND           | 14   | 16 V       |

| Duty cycle                     |                  | 0    | 1          |

| Total external gate resistance | (Note 3)         | 1.7  | Ω          |

## **Electrical Characteristics**

Unless otherwise specified, all data refer to a primary supply voltage of 15V and an ambient temperature of +25°C. Minimum and maximum values refer to the specified maximum rated operating range at ambient temperature.

| Power supply                        | Condition/remark  | Min.  | Тур.  | Max. U | Jnits |

|-------------------------------------|-------------------|-------|-------|--------|-------|

| Primary supply current              | Without gate load |       | 55    |        | mA    |

| Secondary supply voltage V(Cs, COM) |                   | 15.6  | 16.4  | 16.8   | V     |

| Turn-on gate-to-emitter voltage     |                   | 14.0  | 15.1  | 15.95  | V     |

| Turn-off gate-to-emitter voltage    |                   | -14.0 | -15.1 | -15.95 | V     |

| Power supply monitoring    | Condition/remark           | Min. | Тур.        | Max. Units |

|----------------------------|----------------------------|------|-------------|------------|

| Secondary supply [V(G, E)] | Clear fault state (note 1) |      | <u>11.5</u> | <u>V</u>   |

|                            | Set fault state            |      | <u>10.8</u> | <u>V</u>   |

|                            | Hysteresis                 |      | 0.7         | V          |

| Short-circuit monitoring           | Condition/remark           | Min.        | Тур.        | Max. U      | Inits      |

|------------------------------------|----------------------------|-------------|-------------|-------------|------------|

| Pin REF pull-up resistor to pin Cs |                            | 1425        | 1500        | 1575        | Ω          |

| Pin REF source current             | From Cs (note 5)           |             | <u>150</u>  |             | μ <u>Α</u> |

| Pin ME pull-up resistor to pin Cs  | (Note 5)                   | <u>2090</u> | <u>2200</u> | <u>2310</u> | Ω          |

| Pin ME on-state source current     | From Cs (note 5)           |             | <u>1.4</u>  |             | <u>mA</u>  |

| Pin ME off-state sink current      | Towards COM                | 80          |             |             | mΑ         |

| Pin ME off-state resistance        | Towards COM                |             |             | 125         | Ω          |

| Pin REF on-state reference voltage | Functional limits (note 5) | 2.5         |             | 12.5        | V          |

#### **Command blocking**

When a fault state has been cleared, the next turn-on commands are ignored by the ASIC during the command blocking time to avoid thermal overload of the power MOSFET or IGBT driven by the gate driver.

|                       | Condition/Remark                                  | Min.      | Тур.      | Max. Units   |

|-----------------------|---------------------------------------------------|-----------|-----------|--------------|

| Command blocking time | <u>Factory-set</u><br>(other values upon request) | <u>17</u> | <u>22</u> | <u>27</u> ms |

| Pin IN Command Inputs | Condition/Remark         | Min. | Тур. | Max. Units |

|-----------------------|--------------------------|------|------|------------|

| Logic level           | Positive-going threshold |      | 10   | V          |

|                       | Negative-going threshold |      | 5    | V          |

| Bias sink current     |                          |      |      | 1 mA       |

| Pin capacitance       |                          |      |      | 3 pF       |

#### **Pin SO Status Outputs**

Secondary-side faults cause the channel to turn off immediately. Fault states are transmitted to the primary side via the signal transformer interface (option T) or via an optocoupler (option C), in the latter case with an additional delay. Secondary-side faults are then reported at Pin SO.

|                               | Condition/Remark                 | Min.       | Тур.        | Max. U    | nits      |

|-------------------------------|----------------------------------|------------|-------------|-----------|-----------|

| Available current at pins SO  | [V(VCC) - 1.2V] > V(SO+) > V(SO) | )-)        |             |           |           |

|                               | Fault state                      |            |             | 1         | μΑ        |

|                               | Otherwise                        | 1000       |             |           | μΑ        |

| Delay to report a fault state | Option T:                        |            |             |           |           |

|                               | during command blocking time     | <u>Unt</u> | il next cha | nge at IN | <u> *</u> |

|                               | Option C                         |            | 20          |           | μs        |

| Timing Characteristics     | Condition/Remark        | Min. | Тур. | Max. Units |

|----------------------------|-------------------------|------|------|------------|

| Equiv. delay time (note 4) | IGBT turn-on, option N  |      | 300  | ns         |

|                            | IGBT turn-off, option N |      | 350  | ns         |

|                            | IGBT turn-on, option I  |      | 315  | ns         |

|                            | IGBT turn-off, option I |      | 365  | ns         |

| Equiv. rise time (note 4)  | IGBT turn-on            |      | 100  | ns         |

| Equiv. fall time (note 4)  | IGBT turn-off           |      | 80   | ns         |

Data refer to a gate charge of  $1.2\mu C$  and a total external gate resistance of  $5.6\Omega$ .

| Electrical Insulation               | Condition/Remark                  | Min.      | Тур. | Max. Units           |

|-------------------------------------|-----------------------------------|-----------|------|----------------------|

| Operating voltage                   | For option T; continuous (note 6) |           |      | 1500 V <sub>DC</sub> |

| For option C; continuous (note 6)   |                                   |           | 600  | $1000 V_{DC}$        |

| Permitted d/dt (V <sub>C*E*</sub> ) | Ensured by design                 | 100       |      | V/ns                 |

| Test voltage                        | 50 Hz/1 min (note 7)              |           |      | $4000\;V_{AC,\;eff}$ |

| Partial discharge extinction volt.  | To IEC270 (note 8)                | 1700      |      | $V_{AC, pk}$         |

| Creep path primary-secondary        | Option T                          | <u>19</u> |      | mm                   |

|                                     | Option C                          | <u>8</u>  |      | mm                   |

| Creep path secondary-secondary      |                                   | <u>19</u> |      | mm                   |

#### **Footnotes**

- The unipolar primary supply voltage with a nominal value of V(VCC, GND) = 15.0V is multiplied by a magnetic transformer, resulting in a unipolar secondary power supply voltage with a nominal value of V(Cs, COM) = 16.4V. To provide a bipolar gate-driving voltage with the nominal values of V(G, E) = +15.1V for turn-on and V(G, E) = -15.1V for turn-off, both gate and emitter are switched in full-bridge configuration via biploar junction transistors (providing a total nominal level shift of 1.3V). The primary side is equipped with an automatic power-on reset which clears the fault memories when the supply voltage approaches a specified limit with a maximum value of 13.5V.

- 2) In typical applications (hard-switching topology using recommended gate resistors and gate charge) the switching frequency is primarily limited by the switching losses of the IGBT module or by the gate power due to the gate charge required by the module. The switching losses of the gate driver depend strongly on the particular operating conditions and increase with reducing the gate resistance and increasing switching frequency. For switching frequencies beyond 20kHz or gate pulse charges > 5.1µC, the thermal limits of the gate driver may be exceeded. A derating of the IGBT's average gate power is required under these estimated exemplary conditions. Conditions other than those specified may affect the reliability or lead to thermal breakdown of the gate drivers. Please ask our support team for a specific estimation. As a rule, the case temperature of any component of the gate driver should stay below 65°C for an ambient temperature of 25°C.

- 3) The total external gate resistance is the sum of the IGBT-internal chip resistances and the externally used gate resistors. Note that the driver-internal minimum resistance is below  $0.2\Omega$ . Due to the finite slew rate of the driver output voltage and to parasitic inductances in the gate control loop, however, the resulting gate current may not approach the nominal maximum value of 16A.

- 4) Equivalent delay, rise or fall times are derived from comparisons with the results obtained when modeling the driver as an ideal pulse-shaped voltage source with no delay and an infinite slew rate.

- 5) At the REF pin, a  $1.5 \text{ k}\Omega$  resistor is connected to the positive voltage terminal Cs of the secondary-side power supply in parallel with a nominal  $150\mu\text{A}$  current source. The reference voltage may be set via an external Zener diode or an external resistor connected to pin E. Furthermore, at pin ME a  $2.2 \text{ k}\Omega$  resistor is connected to Cs in parallel with a nominal 1.4mA current source.

- 6) Maximum continuous, or repeatedly applied DC voltage or peak value of the repeatedly applied AC voltage between any primary-side pin and any secondary-side pin. **Caution for option C:** operating voltages exceeding 600V may degrade the long-term characteristics of the optocouplers, resulting in an increased delay or a reduced current capability at pin SO.

- 7) The test voltage of 4000 Vac(rms)/50 Hz may be applied only one time and for one minute. It should be noted that with this (strictly speaking obsolete) test method, some (minor) damage

occurs to the insulation layers due to the partial discharge. Consequently, this test is not performed at CONCEPT as a series test. Where repeated insulation tests (e.g. module test, equipment test, system test) are run, the subsequent tests should be performed at a lower test voltage: the test voltage is reduced by 400 V for each additional test. The more modern if more elaborate partial-discharge measurement is preferable to such test methods as it is almost entirely non-destructive.

- 8) The partial discharge test is performed for each driver within the scope of series production. This constitutes a high voltage testing rate of 100% in series production.

- 9) The supported gate charge refers to the stability of the power supply voltages and to the dynamic voltage drop at the supply rail. Exceeding the maximum supported gate charge may lead to malfunction or thermal overload of the gate drivers. The customer may increase the specified maximum value of the supported gate charge by connecting additional supply capacitors between terminals Cs and COM up to a total of  $100\mu\text{F}$ . External blocking capacitors must be applied for pulse gate charges >5.1 $\mu$ C. The capacitance rating must be greater or equal  $2\mu\text{F}$  per  $1\mu\text{C}$  gate pulse charge exceeding  $5.1\mu$ C. Place the capacitors with short traces to the IGD616's pins. Make sure to check your design for the thermal limits given in note 2.

#### **Important Notice**

The data contained in this product data sheet is intended exclusively for technically trained staff. Handling all high-voltage equipment involves risk to life. Strict compliance with the respective safety regulations is mandatory!

Any handling of electronic devices is subject to the general specifications for protecting electrostatic-sensitive devices according to international standard IEC 747-1, Chapter IX or European standard EN 100015 (i.e. the workplace, tools, etc. must comply with these standards). Otherwise, this product may be damaged.

#### **Disclaimer**

This data sheet specifies devices but cannot promise to deliver any specific characteristics. No warranty or guarantee is given – either expressly or implicitly – regarding delivery, performance or suitability.

CT-Concept Technologie AG reserves the right to make modifications to its technical data and product specifications at any time without prior notice. The general terms and conditions of delivery of CT-Concept Technologie AG apply.

## **Technical Support**

CONCEPT provides expert help for your questions and problems:

Internet: www.IGBT-Driver.com/go/support

## Quality

The obligation to high quality is one of the central features laid down in the mission statement of CT-Concept Technologie AG. The quality management system covers all stages of product development and production up to delivery. The drivers of the SCALE series are manufactured to the ISO 9001 standard.

## **Ordering Information**

|                                                                                                                                                                                                                                   | Type designation                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| N, C Non-inverting, optocoupler-assisted driver for 1200V IGB N, T Non-inverting driver for 1200V or 1700V IGBTs I, C Inverting, optocoupler-assisted driver for 1200V IGBTs I, T Inverting driver for 1200V or 1700V IGBTs Other | Ts IGD616NC1 IGD616NT1 IGD616IC1 IGD616IT1 Upon request |

|                                                                                                                                                                                                                                   | •                                                       |

## **Information about Other Products**

#### For other drivers and evaluation systems

Internet: www.IGBT-Driver.com

#### Manufacturer

CT-Concept Technologie AG Intelligent Power Electronics Renferstrasse 15 CH-2504 Biel-Bienne Switzerland

Tel. +41 - 32 - 344 47 47 Fax +41 - 32 - 344 47 40 E-mail Info@IGBT-Driver.com www.IGBT-Driver.com

© Copyright 1992...2008 by CT-Concept Technologie AG - Switzerland.

All rights reserved.

We reserve the right to make any technical modifications without prior notice.

Version from 2008-04-17